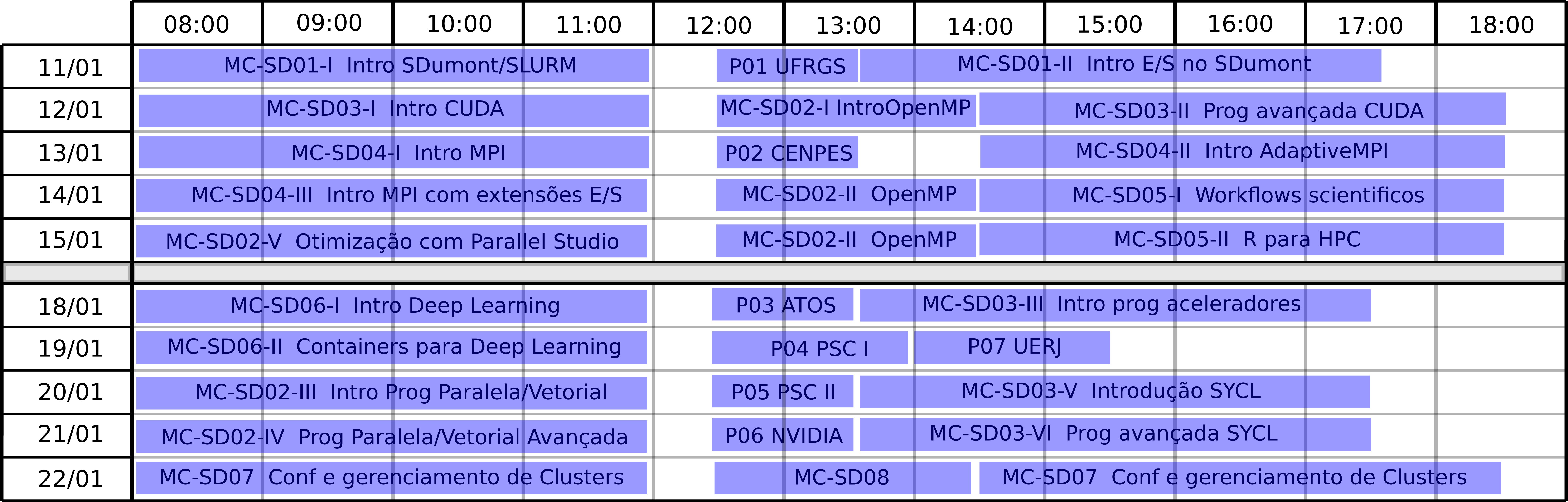

Escola Supercomputador SDumont

11 a 22 de janeiro de 2021

SOBRE O EVENTO

O Supercomputador SDumont atende hoje cerca de 170 projetos de pesquisa pertencentes a 18 áreas de conhecimento, liderados por instituições de pesquisa de 12 estados brasileiros. A escola tem como objetivo prover à comunidade de usuários do Sdumont e à comunidade de programação em computação de alto desempenho em geral, minicursos relacionados com programação em computadores de alto desempenho tais como modelos de programação paralela, ferramentas de perfilagem e bibliotecas para o desenvolvimento de algoritmos paralelos otimizados.

A edição 2021 da Escola SDumont contará com uma programação intensa de 22 minicursos, distribuídos em 8 módulos, e 6 palestras. As atividades serão ministradas por pesquisadores e colaboradores do LNCC, além de contar também com a participação de convidados das seguintes empresas e instituições de pesquisa: ATOS, CENPES-Petrobras, NVIDIA, NVIDIA-Mellanox, Costa Rica National High Technology Center, entre outras.

Organização

- Carla Oshtoff Ferreira de Barros - LNCC

- Roberto Souto - LNCC

Importante

- Material da Escola: O material utilizado durante a Escola SDumont (slides, videos e códigos) encontra-se disponível no seguinte link.

- Inscrições nas atividades da Escola Santos Dumont: acontecerão no período de 01 de dezembro de 2020 a 05 de janeiro de 2021 na aba Incrições.

- Formato da apresentação dos minicursos: Os minicursos serão ministrados na forma síncrona/online, pela plataforma Zoom, em data e horários específicos para cada minicurso.

- Informações detalhadas da programação encontram-se abaixo. Toda a programação da Escola SDumont será gravada e disponibilizada, após o encerramento do Programa de Verão 2021, no canal YouTube do LNCC.

PROGRAMAÇÃO

PALESTRAS

[P01-SD] A Convergência do Big Data com HPC

- Apresentador: Philippe Navaux (UFRGS)

- Horário: Segunda 11/01 às 12:30h

- Resumo: O mundo esta na era do Zetta 1021 dados manipulados/armazenados, indo para o limiar da era do Yotta 1024 dados. Tal quantidade grande de dados, conhecido por Big Data, necessita de tratamento por sistemas não tradicionais para manipulação, análise e extração de informações deste conjunto de dados. Em 1997 foi a primeira vez que foi empregado o termo Big Data referindo-se ao crescente número de dados gerados a cada segundo no mundo de forma estruturada ou não estruturada. Para extrair informações deste Big Data somente é possível empregando máquinas com grande capacidade de processamento paralelo, máquinas HPC, High Performance Computing, traduzindo, máquinas com Processamento de Alto Desempenho. Nesta palestra serão apresentadas as ideias básicas da área de HPC e Big Data mostrando que um depende do outro para manejar todos estes dado e que existe uma convergência entre as áreas.

Possui graduação em Engenharia Elétrica pela Universidade Federal do Rio Grande do Sul(1970), especialização em Engenharia Nuclear pela Universidade Federal do Rio Grande do Sul(1970), mestrado em Física pela Universidade Federal do Rio Grande do Sul(1973) e doutorado em Informática pela Institut National Polytechnique de Grenoble(1979). Atualmente é Coordenador da Área da Computação do CNPq, professor titular da Universidade Federal do Rio Grande do Sul, Consultor do Conselho Nacional de Desenvolvimento Científico e Tecnológico, Consultor da Financiadora de Estudos e Projetos, consultor do Fundação Carlos Chagas Filho de Amparo à Pesquisa do Estado do RJ, Consultor do Fundação de Amparo à Pesquisa do Estado de Alagoas, Consultos do Fundação de Amparo à Pesquisa do Estado de São Paulo, Consultor do Fundação de Amparo à Ciência e Tecnologia do Estado de Pernambuco, Consultor do Fundação de Amparo à Pesquisa do Estado de Minas Gerais, Avaliador da Department of Energy, Avaliador da Agence Nationale de la Recherche, membro Scientific Board -Projeto Com Européia do Projeto Visionair, Membro de corpo editorial da Parallel Computing, Membro de corpo editorial da International Journal of High Performance Systems Architecture (Print), Revisor de periódico da Cluster Computing, Revisor de periódico da VLSI Design, Revisor de periódico da Microprocessors and Microsystems, Revisor de periódico da Interna tional Journal of Parallel Programming, Revisor de periódico da Journal of Network and Computer Applications, Membro de corpo editorial da Communications in Computer and Information Science (Print), Membro do Conselho do Centro de Integração Empresa Escola do RS, Membro da Diretoria - Vice-Presidente do Centro de Integração Empresa Escola do RS e Membro do Conselho do Fundação Luiz Englert. Tem experiência na área de Ciência da Computação, com ênfase em Sistemas de Computação. Atuando principalmente nos seguintes temas:Arquitetura de Computadores, Processamento Paralelo, Banco de Dados. Pesquisador nível 1 do CNPq. Publicou mais de 400 artigos em periódicos e conferências. Orientou cerca de 100 alunos no mestrado e doutorado.

[P02-SD] Desenvolvimento de Solver Paralelo em Arquiteturas Híbridas para Simulações de Fluxo e Geomecânicas em Reservatórios de Petróleo

- Apresentador: Jose Roberto Rodrígues (Cenpes)

- Horário: Quarta 13/01 às 12:30h

- Resumo: A simulação de reservatórios é um componente crucial de quase todas as decisões na indústria de produção de petróleo. Uma operação fundamental desses simuladores é a solução de sistemas de equações lineares de grande porte, que normalmente é a etapa que requer a maior quantidade de recursos computacionais. Depois de revisar brevemente as técnicas usadas para modelar a produção de petróleo e como elas levam à necessidade de resolver grandes sistemas lineares, serão apresentados os principais aspectos levados em consideração em um solver linear dedicado para aplicações em petróleo em desenvolvimento conjunto por equipes da Petrobras e de universidades brasileiras. Serão enfatizados os aspectos de projeto do solver que o permitem rodar com eficiência em uma ampla variedade de plataformas, de estações de trabalho a clusters de nós multicore, com ou sem GPUs, e listadas as principais técnicas numéricas implementadas. Resultados para problemas da ordem de bilhões de incógnitas, rodando em centenas de núcleos computacionais, serão mostrados, comprovando a boa escalabilidade paralela e a competitividade com as melhores opções disponíveis.

José Roberto P. Rodrigues é consultor sênior na gerência de Engenharia de Reservatórios do Centro de Pesquisas da Petrobras (CENPES). Ao longo da sua carreira, trabalhou em diversos aspectos da área de simulação de reservatórios, incluindo solvers lineares e não lineares, problemas inversos, otimização e modelagem de experimentos laboratoriais. Nos últimos anos, tem se dedicado à aplicação de Computação de Alto Desempenho à simulação de reservatórios. É bacharel, mestre e doutor em matemática pela Universidade Federal do Rio de Janeiro (UFRJ).

[P03-SD] SMC: An Atos solution for HPC infrastructure

- Apresentador: Giacomo Mc Evoy Valenzano (ATOS)

- Horário: Segunda 18/01 às 12:30h

- Resumo: The Smart Management Center (SMC) is the newest software management stack for supercomputers, and is based on open source upstream project BlueBanquise. It provides a solution to deploy, update, maintain and manage HPC systems software up to 1200 nodes with very low technical requirements on daily administration tasks.

In this presentation, we will review many technical details about the SMC software stack and show a live installation of its open source components from BlueBanquise. Finally, we will get a glimpse of the next iteration of automatized management, currently under development and designed to enable the exascale-ready BullSequana XH2000 supercomputer architecture.

- Apresentador: John Urbanic (Pittsburgh Supercomputing Center - PSC)

- Horário: Terça 19/01 às 12:30h

- Resumo: In this talk John Urbanic, Parallel Programming Scientists at the Pittsburgh Supercomputing Center, will discuss the future roadmap of High Performance Computing, motivated by our present and developing technologies. The end of Moor’s Law, and the dawning of the Exascale era, present many opportunities. John will discuss the technical challenges that drive the design of these machines at the largest scale, as well as future advances that may change the roadmap. Far from theoretical, these issues inform the choices you make today regarding application development.

- Apresentador: John Urbanic (Pittsburgh Supercomputing Center - PSC)

- Horário: Quarta 20/01 às 12:30h

- Resumo: In this talk John Urbanic, Parallel Programming Scientists at the Pittsburgh Supercomputing Center, will talk about the many parallel programming techniques available today, and then focus on those that are practical to use. This will include most of the approaches taught this week, but at a higher level and more comparative manner. John will explain the strengths, weaknesses and future prospects of these paradigms based on his long experience at scaling up applications from many domains. Questions, discussion and debate are very welcome.

O pesquisador é especialista em pesquisa na área de Computação Paralela e Concorrente. Em particular, em computação de alto desempenho e tecnologias extremamente escaláveis, incluindo as extensões aos modelos de programação MPI, OpenMP, OpenACC e extensões de linguagens de programação em threads e aplicação de técnicas de modelagem e de otimização de desempenho em ambientes de programação de Big Data tal como o Spark e nos novos ambientes de Aprendizado de Máquina e de Deep Learning.

[P06-SD] New DPU helping HPC world

- Apresentador: Richard Graham (NVIDIA - Mellanox)

- Horário: Quinta 21/01 às 12:30h

- Resumo: A DPU is a new class of programmable processor that combines three key elements. A DPU is a system on a chip, or SOC, that combines: An industry standard, high-performance, software programmable, multi-core CPU, typically based on the widely-used Arm architecture, tightly coupled to the other SOC components. A high-performance network interface capable of parsing, processing, and efficiently transferring data at line rate, or the speed of the rest of the network, to GPUs and CPUs. A rich set of flexible and programmable acceleration engines that offload and improve applications performance for AI and Machine Learning, security, telecommunications, and storage, among others. All these DPU capabilities are critical to enable an isolated, bare-metal, cloud-native computing that will define the next generation of cloud-scale computing.

Gilad Shainer serves as senior vice president of marketing for Mellanox networking at NVIDIA, focusing on high performance computing, AI and InfiniBand technology. Gilad joined Mellanox in 2001 as a design engineer and has served in senior marketing management roles since 2005. He serves as the chairman of the HPC-AI Advisory Council organization, the president of the UCF and CCIX consortiums, a member of IBTA and a contributor to the PCISIG PCI-X and PCIe specifications. Gilad holds multiple patents in the field of high-speed networking. He is a recipient of the 2015 R&D100 award for his contribution to the CORE-Direct In-Network Computing technology and the 2019 R&D100 award for his contribution to the Unified Communication X (UCX) technology. Gilad holds an Master of Science and Bachelor of Science in electrical engineering from the Technion Institute of Technology in Israel.

[P07-SD] Exploiting Concurrency in GPUs

- Apresentador: Cristiana Bentes (UERJ)

- Horário: Terça 19/01 às 14:00h

- Resumo: Graphics Processing Units (GPUs) have proven to be a powerful and efficient platform to accelerate a substantial class of compute-intensive applications. For this reason, many large scale data centers are based on heterogeneous architecture comprising multicore CPUs and GPUs to meet the requirements of high performance and data throughput. GPUs are also being used in computational clouds. Exploring GPUs in clouds, through GPU virtualization, allows physical devices to be logically decoupled from a computational node and shared by any application, resulting in monetary costs reduction, energy savings and more flexibility. In this scenario, efficiently sharing a GPU across different applications is an indispensable feature. In this talk, we will discuss how concurrent kernel execution can improve hardware utilization and system throughput. We will present the current challenges in exploiting this feature in GPUs and discuss our work and contributions in this area.

Cristiana Bentes received the B.S. degree in Mathematics from the Rio de Janeiro State University (UERJ), Brazil, in 1988, with specialization in Computer Science. She received the M.Sc. (1991) and Ph.D. (1998) degrees in Systems Engineering and Computer Science from the Federal University of Rio de Janeiro, Brazil. She is currently Full Professor at the Systems Engineering and Computer Science Department of the State University of Rio de Janeiro, Rio de Janeiro, Brazil. She worked on a number of research projects, collaborating with research groups in Brazil and France. Her research interest are High-performance Computing, Parallel Programming, Novel Parallel Architectures and Cloud Computing. Much of her recent work has been on exploiting the power of GPUs to accelerate a number of applications. She has published numerous journals and conference papers on these subjects, and she is an active member of her research community, co-organizing different HPC conferences.

MINICURSOS

Aviso: Devido a questões de segurança, o acesso ao supercomputador SDumont será mantido apenas para os alunos que já tiverem conta no mesmo.

Apenas os alunos cadastrados como usuários do SDumont poderão acompanhar os exercícios na forma 'online' durante os minicursos da escola.

Demais alunos, caso tenham interesse, poderão acompanhar os exercícios apresentados executando os mesmos nas suas máquinas locais ou computadores das suas universidades.

Módulo 1- Introdução ao Ambiente de programação no SDUMONT

[MC-SD01-I] Introdução ao ambiente SDUMONT /SLURM e Ferramentas de Avaliação de Desempenho BULLX-DE

- Professores : Roberto Souto, Andre Carneiro e Bruno Fagundes (LNCC)

- Dias e Horários: 2a feira (11/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professores : Andre Carneiro e Bruno Fagundes (LNCC)

- Dias e Horários: 2a feira (11/01), das 13:30h às 17:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 2- Programação com Processadores Multicore

[MC-SD02-I] Introdução á Programação com OpenMP

- Professores : Carla Osthoff e Frederico Cabral (LNCC)

- Dias e Horários: 3a feira (12/01), das 12:30h às 14:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Carla Osthoff e Frederico Cabral (LNCC)

- Dias e Horários: De 5a feira (14/01) a 6a feira (15/01), das 12:30h às 14:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Matheus Serpa (UFRGS)

- Dias e Horários: 4a feira (20/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Matheus Serpa (UFRGS)

- Dias e Horários: 5a feira (21/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Frederico Cabral (LNCC)

- Dias e Horários: 6a feira (15/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 3- Programação em GPU

[MC-SD03-I] Introdução á Programação CUDA

- Professor : Roberto Souto (LNCC)

- Dias e Horários: 3a feira (12/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Roberto Souto (LNCC)

- Dias e Horários: 3a feira (12/01), das 14:30h às 18:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Esteban Hernandez

- Dias e Horários: 2a feira (18/01), das 13:30h às 17:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Pedro Pais Lopes (Exaflop)

- Dias e Horários: 3a feira (19/01), das 13:30h às 17:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Amanda Sabatini (LBNL) e Douglas Adriano Augusto (Fiocruz)

- Dias e Horários: 4a feira (20/01), das 13:30h às 17:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Amanda Sabatini (LBNL) e Douglas Adriano Augusto (Fiocruz)

- Dias e Horários: 5a feira (21/01), das 13:30h às 17:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 4- Programação em Ambiente de Sistemas Distribuídos (Supercomputadores e Clusters)

[MC-SD04-I] Introdução Programação MPI

- Professores : Carla Osthoff (LNCC)

- Dias e Horários: 4a feira (13/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Esteban Meneses (Costa Rica National High Technology Center)

- Dias e Horários: 4a feira (13/01), das 14:30h às 18:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : André Carneiro (LNCC)

- Dias e Horários: 5a feira (14/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 5- Programação com Bibliotecas de HPC

[MC-SD05-I] Introdução a workflows científicos paralelos em Python/Parsl

- Professor : Kary Ocaña (LNCC)

- Dias e Horários: 5a feira (14/01), das 14:30h às 18:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : Kary Ocaña (LNCC)

- Dias e Horários: 6a feira (15/01), das 14:30h às 18:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 6- Programação com Ambientes de Deep Learning (DGX-2)

[MC-SD06-I] Introdução à Deep Learning

- Professor : João paulo Navarro (NVIDIA)

- Dias e Horários: 2a feira (18/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

- Professor : João paulo Navarro (NVIDIA)

- Dias e Horários: 3a feira (19/01), das 08:00h às 12:00h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 7- Gerenciamento de Clusters (Sistemas Distribuídos)

[MC-SD07] Introdução à configuração e gerenciamento de Clusters

- Professor : Andre Carneiro e Bruno Fagundes (LNCC)

- Dias e Horários: 6a feira (22/01), das 08:00h às 12:00h e das 14:30h às 18:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »

Módulo 8- InfiniBand In-Network Computing Technology

[MC-SD08] InfiniBand In-Network Computing technology overview and advantages

- Professor : Richard Graham (NVIDIA-Mellanox)

- Dias e Horários: 6a feira (22/01) das 12:30h às 14:30h

- Descrição: Conheça a ementa, objetivos e bibliografia do minicurso clicando aqui »